반도체의 단면에서 확인할 수 있듯이, DRAM이나 NAND의 경우 Transistor의 수도 상대적으로 적을 뿐만 아니라, 회로의 대부분이 Capacitor이기 때문에 이를 형성하기 위한 Dielectric이 주를 이루게 된다. 반면, Logic chip의 경우 Transistor를 제외한 대부분이 구리 배선으로 이뤄져 있습니다.

■ 메탈(Metal) 공정 정의 및 Flow

트랜지스터의 집적도가 높아질수록 배선의 층수가 증가하게 되며, 애플의 최신 AP의 경우 배선층이 15층을 넘어가게 됩니다. 사실상 트랜지스터 형성을 제외하고는 대부분의 공정이 배선공정의 반복인 셈입니다. 트랜지스터에 직접적으로 접하는 금속(M0/M1)의 경우 Al(알루미늄)과 W(텅스텐)을 사용합니다.

Cu(구리)의 경우 트랜지스터로 확산되어 오류(Deep Level Impurity)를 일으킬 가능성이 높아 M2 이후부터 사용하게 됩니다. 한편, 구리는 CVD 공정을 하기 적합한 프리커서가 없고 식각이 어려운 특성에 따라 전해 도금(Electroplating) 이후 CMP 공정을 통해 평탄화 하는 다마신(Damascene)공정을 통해 박막을 형성하게 됩니다. 이번 섹션에서는 구리의 전해 도금 공정을 위주로 다루겠습니다.

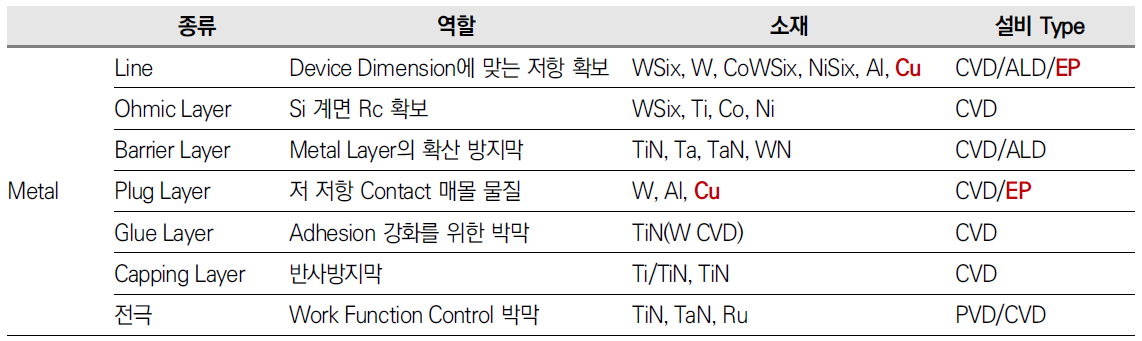

■ 반도체 공정에서 쓰이는 Metal 박막의 종류와 역할

■ 구리 전해도금(Electroplating) 공정 개요

(Hole이나 Trench에 전해도금을 하기에 앞서, CVD/ALD 등을 이용해 Ta(탄탈륨)/TaN를 먼저 증착해줍니다. Ta/TaN은 구리가 유전막 등으로 확산되어 소자에 오류를 유발하는 것을 방지하는 확산 방지막(Diffusion Barrier)의 역할을 합니다. 또한, Ta는 TaN이 표면에 접착할 수 있도록 하는 역할 (Glue Layer)을 한다. Ta/TaN 표면은 전해 도금을 하기에는 저항이 크기 때문에 구리 씨앗층(Cu Seed Layer)을 형성시켜야 합니다.

구리 같은 경우에는 CVD 공정에 맞는 Precursor가 없기 때문에 PVD 방식을 이용해 물리적으로 도포하게 됩니다. 이후 ECD(Electro Copper Deposition) 장비에서도금액에 담가 도금 과정을 진행합니다.

한편, 전해도금을 통해 Trench나 Via를 채우는 과정에서 구리가 불균일하게 차오르거나 동시에 Conformal 하게 차오르는 경우 Void나 Seam이 발생하게 되며, 이는 소자의 신뢰성과 성능을 저하시키는 요인이다. 불균일 차오름이 일어나는 원인은 구리의 도금 속도가 위치마다 다르기 때문입니다.

이를 조절하기 위해 가속제(Accelerator), 억제제(Suppressor), Leveler 등을 첨가해 균일한 바닥차오름(Super Conformal)을 실현하게 됩니다. 가속제는 바닥에서의 도금을 가속화하고, 억제 제는 입구 부위의 도금을 저지하는 원리로 바닥에서부터 차오를 수 있도록 하는 원리입니다.

'반도체' 카테고리의 다른 글

| 반도체 전공정 - 세정(Cleaning)공정 (0) | 2022.06.18 |

|---|---|

| 반도체 전공정 - 평탄화(CMP)공정 (0) | 2022.06.18 |

| 반도체 전공정 - 증착(Deposition)공정 (0) | 2022.06.18 |

| 반도체 전공정 - 확산/열처리(Diffusion/Thermal)공정 (0) | 2022.06.18 |

| 반도체 전공정 - 습식 식각(Wet Etching)공정 (0) | 2022.06.18 |

댓글